Technology

Advanced Technologies for IP and FPGA Verification

Blue Pearl Software is an electronic design automation (EDA) company that offers a unique and powerful approach to improving the process of designing computer chips or integrated circuits (ICs) which power electronic systems such as iPOD’s, cell-phones, PDA’s, and PC’s. The convergence of computer, communications and consumer markets drives greater functionality chips that use continually improving fabrication technologies which allow hundreds of millions of transistors to be integrated on a single silicon chip cost effectively, posing significant design challenges.

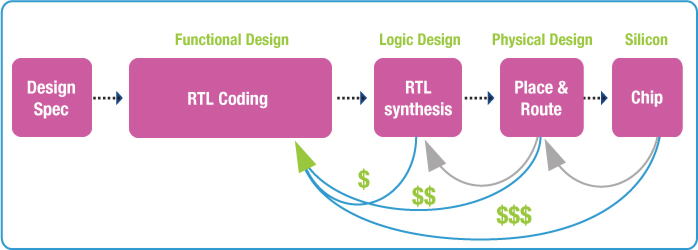

It is best to implement a new chip design from an accurate specification and allow the tools in the ASIC or FPGA chip design flow to follow the comprehensive and complete specifications. The decreasing technology dimensions and continually increasing complexity of chips that are being designed are both causing significant iterations in chip design flows, increasing design costs and delaying chip developments. The delayed or unpredictable development times are a major cause of concern to designers and companies, so Blue Pearl is focusing its proprietary technologies to provide automated tools to reduce iterations and make the chip design flow more predictable.

The proprietary technologies used by Blue Pearl include RTL analysis, high-level symbolic simulation and state space exploration. These technologies have been developed over many years by the founders of Blue Pearl and are the foundation for existing and future products to address verification needs of large designs at RTL or the functional level.

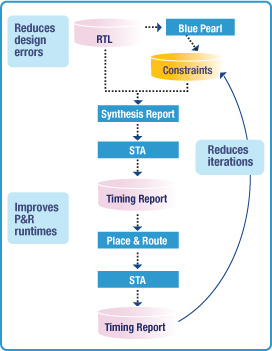

A fundamental bottleneck in the chip design flow is ensuring that chips meet their speed or timing goals. The ability of a chip to perform its functional operations within a specified amount of time is determined by critical electrical paths. Significant manual effort and time is expended by designers and verification engineers to identify these critical paths and then generate the timing constraints, which drive the tools in the development flow to meet the timing or speed required. Blue Pearl speeds up the process of ensuring designs meet their timing requirements by automatically generating optimal timing constraints at the functional or register transfer level (RTL). The automated tools generate the timing constraints very early in the design cycle where they provide the most benefit. The breakthrough technologies developed by Blue Pearl give designers the ability to analyze the intended functionality of the chip based on the high-level RTL description, and automatically determine the paths through the design that do not affect timing or speed of operation (called false or multi-cycle paths). Timing constraints are then automatically generated.

The technologies are scaleable and can be applied to many compelling issues at the functional stage. The inputs and outputs of our tools are all industry standards and allow seamless integration with existing design flows and tools. The technologies have been fine-tuned to operate at the functional level rather than the structural or gate level, where most of the competition operates. Blue Pearl therefore provides the advantages of working on large designs at the full chip level much faster than other tools. Blue Pearl is ensuring that the tools are easy to learn and use. These advantages can be carried forward into support of even higher levels of abstraction such as SystemC, which is the emerging language for electronic system level (ESL) design and, is one of the fastest growing segments in EDA.