Advanced Clock Environment (ACE)

Overview

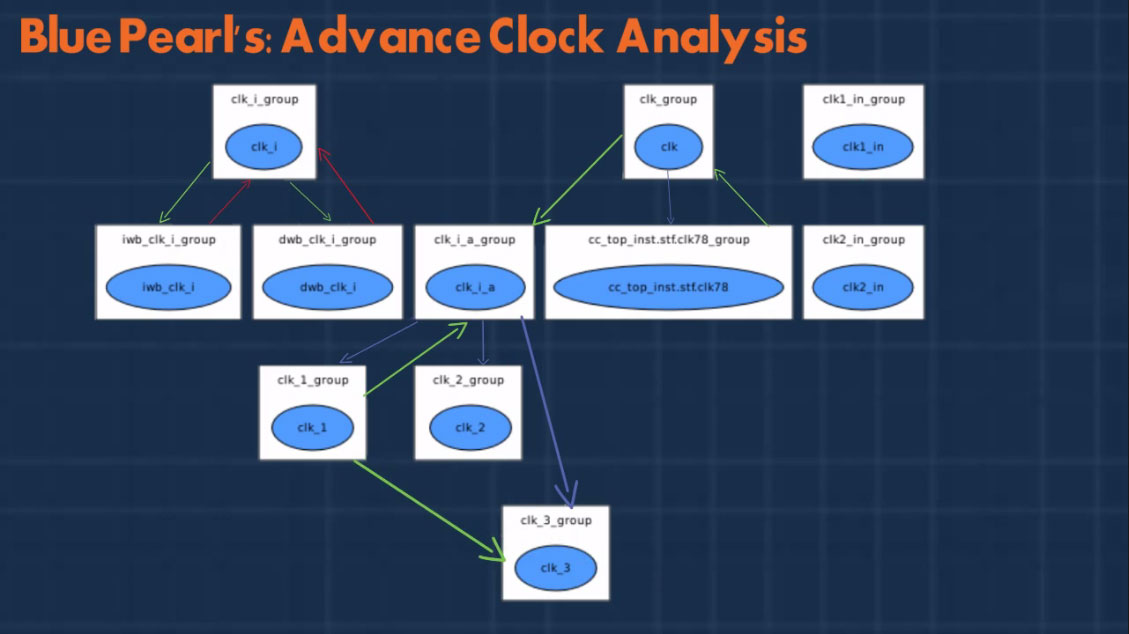

Blue Pearl Software’s ACE offers the capability to visualize clocks and asynchronous clock domain crossings in RTL designs to help users analyze their design for CDC metastability.

The Advanced Clock Environment (ACE) tool solves the iterative and reactive CDC setup problem experienced by designers. It is used before running a CDC analysis. With ACE, designers can clearly see if clocks are not in the intended domains and make corrections before in-depth CDC analysis.

Why Advanced Clock Environment (ACE) for CDC Analysis?

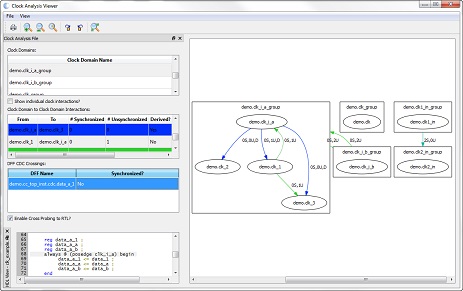

Blue Pearl Software’s Advanced Clock Environment provides a graphical representation summarizing data paths between clocks, and can make recommendations for grouping of clocks into clock domains. With ACE, designers can identify clocks to better understand how they interact with synchronizers in the design. This allows users to quickly identify improper synchronizers or clock domain groupings that cause CDC metastability.

What can I do with ACE?

- Evaluate clock domain definitions

- Evaluate SDC clock constraints

- Generate a graphical analysis of clock and clock domains

- Validate clock grouping recommendations

- Generate SDC template to be used by a CDC analysis tool

To Learn More, Download the Advanceed Clock Environment Datasheet

Download Visual Verification Suite and request your 45 day Starter Edition license and get started today