Company

Company Overview

Blue Pearl Software, Inc. provides products that check digital design issues at the functional or register transfer level (RTL) of the chip design flow. These issues include clock domain crossings (CDCs), synthesis vs. simulation mismatches, inadvertent latch generation, coding style and conventions, and basic linting, as well as verifying conformance with design standards such as DO-254, STARC, and RMM. Blue Pearl’s software is used by ASIC and FPGA designers early in the design flow on high-level functional design descriptions of an integrated circuit (IC), to develop higher quality RTL code, and can also automatically generate comprehensive and accurate timing constraints that significantly improve quality of results (QoR). Our customers can significantly reduce time to market, lower design costs, and make the design development schedule more predictable. Incorporating Blue Pearl’s products in the design flow is easy as all inputs and outputs are industry standards.

Value in Market

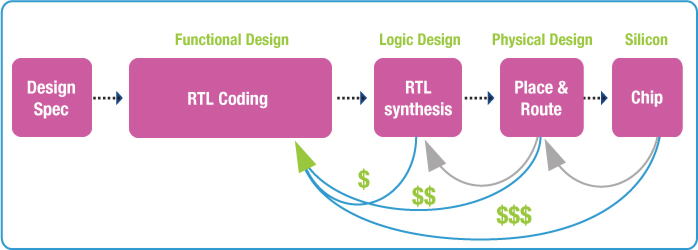

The ASIC and FPGA chip design flows are top-down design flows where the specification drives the implementation through synthesis and place and route (P&R) to a mask set for silicon manufacturing. Designers interpret the chip specification and code the functional design by writing in a high-level design language (HDL) such as Verilog or VHDL at the register transfer level (RTL). Designers and verification engineers using RTL tools represent the largest market for software tool seats in EDA; ~82% of total seats.

Automating Critical Manual Processes

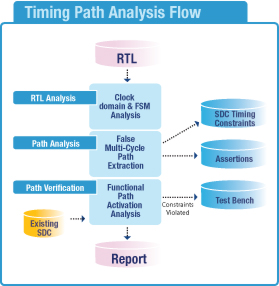

Blue Pearl provides products that automate manual, error prone processes at the functional design stage. We validate that design specifications are met at the register transfer level (RTL) so that downstream tools in the chip design flow have the directives needed to synthesize and implement the design. Analyze RTL™ checks functional design integrity and conformance to rules and methodology. Blue Pearl Software™ identifies timing exception paths and creates an SDC file for implementation. Blue Pearl’s innovative technology tools accelerate design implementation and improve product quality by enabling fixes to issues early, when they are easiest and quickest to fix, so lowering the overall design cost and making the design process more predictable.

Due to advancing technology into smaller nanometer dimensions, hundreds of millions of transistors can be integrated onto a chip that can be manufactured with high yields. The convergence of consumer, communications and computing markets has also driven the functionality that can use these vast numbers of transistors. However, designers are faced with ever increasing complexity for chip design. Design of complex chips in advancing technologies has produced the need for more EDA tools and better methodologies as design cycles have increased with more and more iterations in the chip design flow. The design of a complex chip in 90nm technology can cost between $20 – $30 million! Improvements in methodology are needed to make the design cycle more productive and lower the cost of designs.

Blue Pearl Software has developed tools that automate manual tasks at the RTL or high-level, at the front-end of the flow. By validating timing constraints, generating complete timing constraints for false and multicycle paths and reporting on functional design issues, problems can be fixed early before synthesis and physical implementation processes, reducing the number of iterations in the flow considerably. Iterations can take between 1 – 4 weeks depending on how late in the flow an issue is found and use of Blue Pearl Software’s tools, can save $500K to $1.5M for a single iteration. Customers benefit from a very large return on investment when using Blue Pearl Software’s products and also gain more predictability when launching new products targeted at narrow market windows.