Automatic SDC Generation

Overview

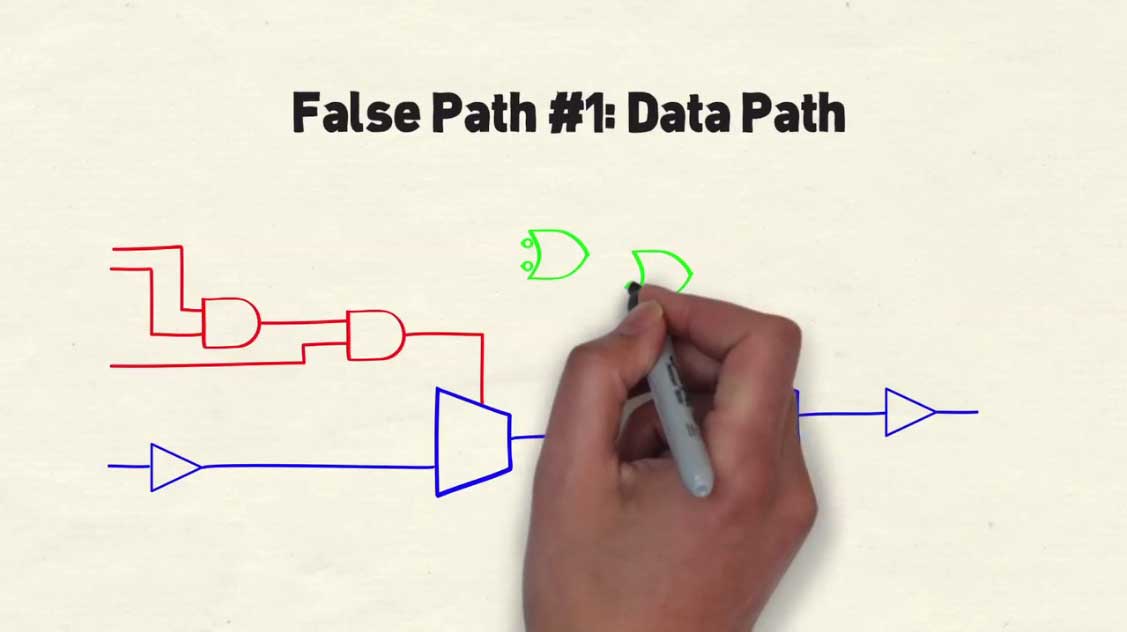

ASICs and FPGAs have many false paths and multi-cycle paths that implementation tools attempt to optimize to make timing goals. These paths can cause the critical paths to miss timing, and waste run time and system memory. Adding false path constraints frees up the synthesis tool to work only on necessary paths that will give better results for a design. Blue Pearl offers a way to automate false path generation that can be run after design changes. In a typical design, there may be a significant number of false paths or multi cycle paths. Passing all of them to synthesis or place & route can be very expensive and taxing to these tools. Blue Pearl’s smart SDC generation limits the number of exceptions generated, reads in critical paths information and accepts multiple formats.

Why Create Timing Constraints?

Features

- Fast FSM and control behavior analysis

- Sequential analysis of false and multi-cycle paths

- Generates timing exception constraints for:

- – Capitalize signals in signals crossing clock domains

- – Resets and constrained signals

- – Configuration registers

- – Functional false paths (FPs)

- – Multicycle paths (MCPs)

- – Block level MCPs where cyclic signalsemanate from block ports

- Compares constraints in different SDC files

- Migrates block constraints to top-level constraints

Accelerates Timing Closure

Blue Pearl’s SDC will automatically find the timing exceptions, that is, the false paths and multi cycle paths, and provide that information to the implementation tools. Other features that help with timing closure are max fanout checks, if-then-else depth and longest path capability.

Find the Exceptions that Matter

There are many more false paths in a design than implementation tools can effectively use. When input as timing exception constraints, implementation tools will often use excessive memory, runtime or ignore constraints beyond some number. Blue Pearl has the ability to input critical path timing reports from static timing analysis tools, identifying select areas of the design generating false paths.

To Learn More, Download the SDC Generation Datasheet

Download Visual Verification Suite and request your 45 day Starter Edition license and get started today