Working with ASIC and particularly FPGA designers, I’m frequently asked if finding bugs using existing simulation or emulation tools is sufficient. The short answer is “Yes”,but it’s not always the most efficient. As design sizes increase but schedules do not expand to match, designers find themselves frustrated by spending too much time looking at simulation results or on bench testing to find bugs. Recently a mil aerospace customer lamented that, aside from enduring the process of re-planning and resetting schedules, and the risk of having a project cancelled for being 2+ weeks late, it’s very embarrassing to explain to management that the mistake turned out to be just some unconnected nets that could easily have been found by a lint tool in mere minutes.

Working with ASIC and particularly FPGA designers, I’m frequently asked if finding bugs using existing simulation or emulation tools is sufficient. The short answer is “Yes”,but it’s not always the most efficient. As design sizes increase but schedules do not expand to match, designers find themselves frustrated by spending too much time looking at simulation results or on bench testing to find bugs. Recently a mil aerospace customer lamented that, aside from enduring the process of re-planning and resetting schedules, and the risk of having a project cancelled for being 2+ weeks late, it’s very embarrassing to explain to management that the mistake turned out to be just some unconnected nets that could easily have been found by a lint tool in mere minutes.

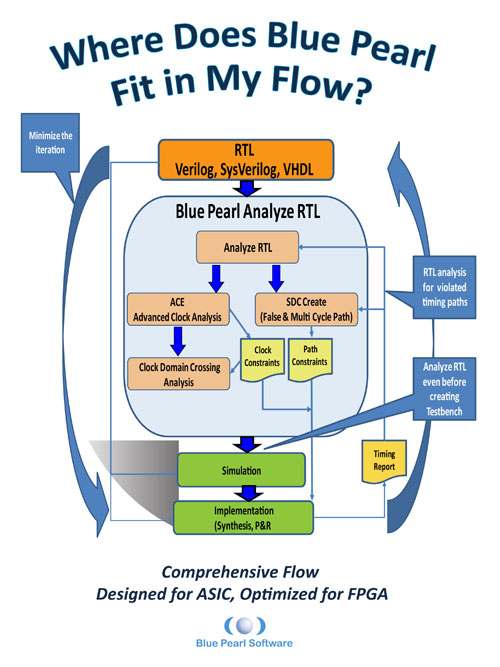

That is why customers now rely on lint or structural analysis tools like the Blue Pearl Software Suite in order to accelerate their IP and FPGA designs. Our tool suite includes RTL design analysis – linting, clock domain crossing (CDC) analysis and automatic timing constraint (SDC) generation.

We analyze the Verilog or VHDL and looks for situations that can cause design failures, such as a net that is undriven. This could cause an unknown state that would have to be debugged through a simulation wave forms viewer. A CDC crossing without a synchronizer will cause design failures that simulators might never catch at all.

Naturally, the next question I’m frequently asked is how and where Blue Pearl fits in one’s design flow:

- Before Simulation –Blue Pearl can be used after initially writing the code. By using Blue Pearl to find design errors in the code, the designer can quickly check the language compliance and look for errors that can cause simulation failures. These errors can be found before developing a testbench.

- Before Synthesis – Blue Pearl looks for code that could be un-synthesizable or could cause post-synthesis simulation results that are different from pre-synthesis simulation.

- When generating constraints – After clock domain crossing synchronization has been added,Blue Pearl shows a visualization of the clocks and clock domains to help the user generate correct clock and clock domain constraints.

- After CDC Synchronization Insertion –Blue Pearl looks for Clock Domain Crossing Synchronizers and determines where they are missing.

- After Synthesis–Once it has been implemented,Blue Pearl can be used to visualize the RTL that caused a violated timing path. This can be done using a timing report that identifies the violated timing paths.

Blue Pearl can be used to easily and quickly find bugs that can hold up the design process. This is done early in the flow, when code is just being written, and after it has been implemented and when ECOs changes have to be made.

If you have any questions, comments, war stories, or compliments, please feel free to drop me a line. Bart@bluepearlsoftware.com